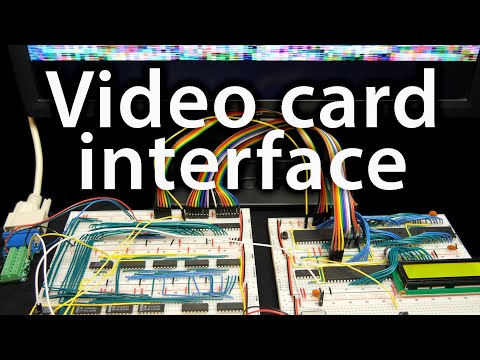

The world's worst video card?

Ben Eater・39 minutes read

VGA interface has crucial pins for image display, with timing and pixel counting vital for proper functionality and resolution selection on monitors. Building circuits using specific chips and connections is necessary to ensure accurate pixel and line counting, as well as proper timing for horizontal and vertical sync signals.

Insights

- Proper timing of horizontal and vertical sync signals (pins 13 and 14) is crucial for image display, with specific intervals like front porch and back porch essential for beam stabilization on modern flat panel monitors.

- Building precise pixel counters using chips like 74LS161 and implementing strategies like inverted bits fed into NAND gates are crucial for decoding pixel counts accurately and ensuring proper synchronization for display intervals on monitors.

Get key ideas from YouTube videos. It’s free

Recent questions

What are the crucial signals in a VGA interface?

The VGA interface consists of 15 pins, with the most important signals being red, green, blue, horizontal sync, and vertical sync. These signals are essential for proper image display on a monitor.

How do old CRT monitors paint images?

Old CRT monitors utilized electron beams and electromagnets to paint images by scanning from left to right and top to bottom. This scanning process allowed the monitor to display images on the screen.

Why is proper timing of sync signals crucial for image display?

Proper timing of horizontal and vertical sync signals (pins 13 and 14) is crucial for image display on a monitor. Incorrect timing could result in damage to older CRT monitors, affecting the quality of the displayed image.

What is the importance of pixel clock frequencies in monitors?

Pixel clock frequencies in the tens of megahertz are crucial for precise timing of scanline and porch lengths in monitors. These frequencies ensure that the display of pixels on the screen is accurate and consistent.

How do modern flat panel monitors differ from old CRT monitors in terms of timing?

Modern flat panel monitors follow similar timing for pixel display as old CRT monitors, including margins for beam stabilization. However, incorrect timing that could damage older CRT monitors does not affect modern flat panel monitors.

Related videos

Summary

00:00

"VGA Interface Timing and Pixel Display"

- VGA interface has 15 pins, with only 5 crucial signals: red, green, blue, horizontal sync, and vertical sync.

- Old CRT monitors used electron beams and electromagnets to paint images by scanning left to right and top to bottom.

- Modern flat panel monitors follow similar timing for pixel display, including margins for beam stabilization.

- Timing for pixel display includes visible scanline time, front porch, sync pulse, and back porch.

- Proper timing of horizontal and vertical sync signals (pins 13 and 14) is crucial for image display.

- Incorrect timing could damage older CRT monitors, but not modern flat panel monitors.

- Different resolutions and modes require specific timing, with trade-offs in choosing easier-to-build hardware.

- Pixel clock frequencies in the tens of megahertz require precise timing for scanline and porch lengths.

- Building a pixel counter using 74LS161 chips with cascading for counting up to 264 pixels horizontally.

- Detecting specific pixel counts, like 200, using inverted bits fed into a NAND gate to trigger actions like resetting the counter.

10:59

Decoding Numbers with Inverters and Gates

- The overall value is 456, with the 256 place being crucial.

- Reset the counter to zero at 264 to ensure it doesn't exceed 456.

- Detection at 200 and 210 involves examining different bits.

- Matching values to 10 and 242 requires inverting bits strategically.

- For 264, the first bit must be 1, while the last bit can be ignored.

- Inverters are essential for decoding numbers accurately.

- Use 74LS04 chips for inverting signals, requiring two chips for nine inverters.

- Implement NAND gates to decode values like 264, ensuring proper connections.

- Repeat the process for 242, focusing on the top eight bits.

- Detecting 200 and 210 involves setting up additional NAND gates and connecting inputs accordingly.

21:54

"Measuring LED Display Sync Pulse Intervals"

- LEDs appear to be on at 10 megahertz, intervals in microseconds, not visible to the naked eye

- Need to connect oscilloscope to measure exact times of display interval and sync pulse

- Sync pulse should be high then low, check NOT Q output of SR latch for correct sync pulse

- Visible area should be 20 microseconds, sync pulse should be 23.2 microseconds

- Front porch is 1 microsecond, back porch is 2.1 microseconds

- Need to build a circuit counting pixels for horizontal sync signal, 10 bits needed

- Vertical sync signal works similarly, counting scan lines instead of pixels

- Need to build a circuit counting lines, detecting 600, 601, 605, and 628

- Vertical timing circuit requires 10 bits, reset signal from horizontal counter used as clock signal