27c3: Reverse Engineering the MOS 6502 CPU (en)

Christiaan008・47 minutes read

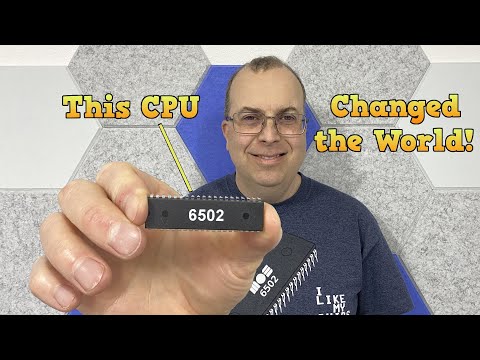

The talk delves into the reverse engineering of the 6502 CPU, highlighting its history, efficiency, and architecture, including addressing modes and instructions. Various aspects of the CPU, like unique decimal mode and illegal opcodes, are discussed, along with efforts to emulate and understand its inner workings through simulators and die shots, aiding in bug detection and validation.

Insights

- The MOS 6502 CPU, known for its efficiency and simplicity, originated from a team that left Motorola to form MOS in 1974, leading to its widespread use in computers, gaming consoles, and even the Terminator series.

- Reverse engineering the 6502 CPU involves detailed analysis of its architecture, addressing modes, stack operations, and peculiarities like the unique decimal mode, utilizing methods like die shots, schematic reconstruction, and physics simulation for accurate emulation, aiding in bug detection and code validation.

Get key ideas from YouTube videos. It’s free

Recent questions

What is the MOS 6502 CPU?

The MOS 6502 CPU is a processor used in Apple II, NES, and C64 known for its efficiency and simplicity.

Who presented the talk on the MOS 6502 CPU?

Michael Style presented the talk on the MOS 6502 CPU.

What are the key features of the MOS 6502 CPU?

The MOS 6502 CPU is known for its efficiency, simplicity, and elegance compared to other processors.

How was the reverse engineering of the MOS 6502 CPU conducted?

The reverse engineering of the MOS 6502 CPU involved die shots, high-resolution photographs, and physics simulation for accurate reconstruction.

What are the implications of the reverse engineering efforts on the MOS 6502 CPU?

Reverse engineering efforts on the MOS 6502 CPU have led to a deeper understanding of its architecture, bug identification, and potential fixes.

Related videos

Summary

00:00

"Reverse Engineering MOS 6502 CPU Efficiency"

- The talk focuses on the reverse engineering of the MOS 6502 CPU used in Apple II, NES, and C64.

- Michael Style presents the talk, titled "Reverse Engineering of the MOS 6502 CPU," with a subtitle of "3510 transistors in 60 minutes."

- The history of the 6502 CPU is discussed, originating from a team that left Motorola to form MOS in 1974.

- The 6502 CPU was widely used in various computers, gaming consoles, and even in the Terminator series.

- The 6502 CPU is highlighted for its efficiency, simplicity, and elegance compared to other CPUs like the Z80.

- The talk is divided into three parts: top-down view of the 6502, bottom-up disassembly, and insights gained from deconstructing the CPU.

- The programming model of the 6502 is explained, detailing registers like the accumulator, index registers, processor status register, program counter, and stack pointer.

- Different addressing modes for instructions are discussed, including immediate, absolute, zero page, and indirect addressing.

- Stack operations are explained, illustrating how pushing and pulling data works implicitly in the 6502 CPU.

- The talk delves into the unique decimal mode of the 6502 CPU, optimizing storage for binary coded decimal numbers.

16:47

"6502 Architecture: Bugs, Easter Eggs, Emulation"

- Bill Gates wrote Commodore licensed Microsoft Basic for the PET, then returned to Microsoft for bug fixes for later versions, leading to Microsoft's displeasure due to the absence of their name in Commodore Basic.

- Microsoft included an Easter egg in the code, believed to be authored by Bill Gates, as Microsoft only had three employees in 1976-77, with one unable to code and another focused on Z80.

- The 8-bit architecture of the system meant every memory access was a single cycle, with instructions like load from zero page taking three cycles, compare taking two, and branch instructions adding an extra cycle if taken.

- Certain instructions, like transfers and loads, required multiple cycles, with more complex operations like an increment of zero page taking five cycles, while an RTS or jump to subroutine combination could consume 12 cycles.

- The 6502 architecture had peculiarities like unexpected behavior when incrementing memory, where the original value was written back before storing the new value, allowing for unique uses in software development.

- A bug existed with the break instruction, where if an interrupt occurred simultaneously, the break would be disregarded, and the interrupt handled instead, raising concerns about the system's reliability.

- The use of illegal opcodes in the 6502 architecture led to varied outcomes, with some opcodes crashing the CPU, others being useful, and extensive research and tables compiled on their effects.

- To understand the CPU's inner workings, one could refer to data sheets, timing diagrams, and schematic diagrams, although discrepancies in the documentation, like missing internal bus details, could complicate the process.

- Reverse engineering the 6502 involved die shots to understand the transistor-level operations, with individuals like Balash from Hungary and the Visual 6502 project reconstructing the CPU's schematic diagram through high-resolution photographs and netlist conversion.

- Emulating the 6502 through physics simulation involved analyzing node potentials, transistor connections, and clock cycles to stabilize the system, offering a unique approach compared to traditional code-based emulators, simplifying complexity and enhancing accuracy.

31:32

Visual 6502 Simulator: Slow but Detailed

- The Visual 6502 simulator in HTML5 is incredibly slow, running at about 2-3 hertz, a million times slower than a real chip.

- An advanced mode allows for a deeper look into the internal workings of the simulator, aiding in understanding complex scenarios.

- A C version of the simulator was developed to improve speed, although it remains significantly slower than real-time.

- Automated testing of op codes, registers, inputs, outputs, and timing is possible with the simulator, aiding in bug detection and code validation.

- The simulator can be used to compare and test various 6502 cores in emulators, helping identify and rectify bugs and edge cases.

- A schematic diagram provides a detailed breakdown of the 6502 CPU structure, highlighting key components like the program counter, sequencer, decoder, registers, and buses.

- The timing generator in the CPU allows for interleaving of instructions, making it memory-bound and fast per cycle.

- The decode ROM in the CPU decodes op codes and cycles, with the G value determining the register being worked on.

- The random control logic in the CPU controls specific components like the ALU and buses, ensuring precise operation.

- The predecode logic in the CPU manages interrupts and resets, injecting a break instruction for proper sequencing, but causing a known bug if an IRQ and break coincide.

45:53

"Sequencer, Knobs, Opcodes: CPU Research Insights"

- The sequencer shifts the one bit to the right, leading to a state where no further instructions can be fetched, causing the machine to be stuck.

- Knobs on the machine control timing, with some, like sax and lax, combining functions for storing and loading data simultaneously.

- Investigation into illegal opcodes is ongoing, with reverse engineering efforts involving multiple individuals on a mailing list and internal wiki.

- Research extends beyond the 6502 CPU to include variations like the one in the NES, with comparisons aiding in bug identification and potential fixes.